Hello-FPGA-FMC-SFP-X4

·Precise Test Adaptation

· Precise Test Adaptation

· Flexible Expansion

Hello-FPGA-FMC-SFP-X4

FMC to 4-Port SFP+ 10G Fiber Interface Card - VITA 57.1 Compliant

| 10Gb/s Per Port | High-Density Expansion

4 Core Advantages

Full Standard Compliance

Strictly compliant with VITA 57.1 standard, adopting FMC LPC (Low Pin Count) connector (Model: ASP-134488-01) with 160 pins design, supporting VADJ adjustable voltage, compatible with mainstream FPGA carrier boards to maximize carrier board reuse rate.

4-Port High-Density Interface

Integrated with 4 independent SFP+ fiber transceiver interfaces, each with dedicated TX/RX differential channels, supporting up to 10Gb/s transmission rate per port. 4-port parallel transmission meets high-density 10G data interaction requirements, suitable for multi-port device interconnection scenarios.

Precision Test Compatibility

Compatible with Xilinx VIVADO development environment, supporting professional debugging tools such as IBERT Bit Error Rate Test, Eye Diagram Scanning, and Jitter Analysis. Target Bit Error Rate (BER) as low as 8.3×10⁻¹², eye diagram opening up to 66.67% UI to ensure test accuracy.

Flexible Expansion & Upgrade

Support SFP+ multi-mode/single-mode optical modules and passive/active Direct Attach Cables (DAC), with flexible transmission distance selection from 1m to 10m; supporting hot-swapping function for maintenance and upgrade without system shutdown; VADJ adjustable voltage (1.2V/1.8V/2.5V) matches different I/O level requirements.

Product Introduction

- Hello-FPGA-FMC-SFP-X4 is a high-density 10G fiber expansion module specially designed for FPGA development. It quickly expands 4 SFP+ fiber interfaces for FPGA development boards through FMC LPC interface, with up to 10Gb/s transceiver rate per port, serving as a core adapter component for 10G high-speed data transmission verification.

- Strictly compliant with VITA 57.1 standard, the product is equipped with dual high-precision crystal oscillators of 125MHz and 156.25MHz to provide stable clock source for timing accuracy; integrated with 24LC04 I2C EEPROM, supporting I²C protocol, which can store board ID, manufacturer information, etc., to realize automatic module identification.

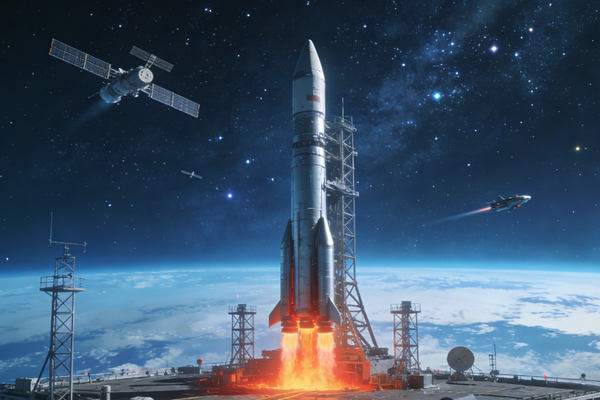

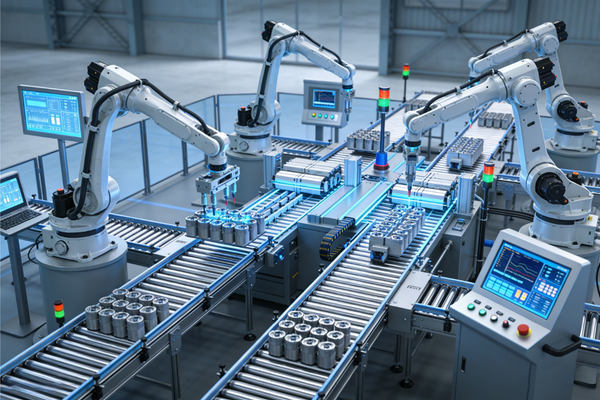

- Specially designed for scenarios such as fiber high-speed communication verification, data center interconnection, and FPGA development testing, it has high compatibility, stability and convenience, and can be widely used in intelligent vehicle, medical equipment, aerospace, industrial automation and other fields.

- As an FPGA I/O expansion tool, the product eliminates the need for professional knowledge of complex protocol standards, reduces power consumption and cost by simplifying system design, shortens engineering design time, and makes FPGA development more efficient.

Hardware Features

- Compliance Standard: Strictly compliant with VITA 57.1 standard, adopting FMC LPC (Low Pin Count) interface, connector model ASP-134488-01 with 160 pins design, supporting VADJ adjustable voltage.

- Interface Configuration: 4 SFP+ fiber transceiver interfaces, each with independent TX/RX differential channels, supporting 10Gb/s high-speed data transmission to meet high-density parallel communication requirements.

- Clock & Storage: Onboard dual high-precision crystal oscillators of 125MHz + 156.25MHz to provide stable clock source; integrated with 24LC04 I2C EEPROM, supporting I²C protocol to realize automatic module identification.

- Compatible Module Types: Optical Modules: SFP+ SR (multi-mode ≤300m), LR (single-mode ≤10km), ER (single-mode ≤40km); Copper Cables: SFP+ DAC (1~10m); supporting hot-swapping.

- Power Supply Compatibility: Supporting +3.3V and +12V power supply provided by carrier board, VADJ adjustable voltage (1.2V/1.8V/2.5V, etc.) matches different I/O level requirements.

- Status Monitoring: Equipped with status detection pins such as TX_DIS and RX_LOSS to monitor link working status in real time, facilitating fault diagnosis and system maintenance.

- Software Compatibility: Compatible with Xilinx VIVADO development environment, supporting professional debugging tools such as IBERT Bit Error Rate Test, Eye Diagram Scanning, and Jitter Analysis.

Technical Specifications

| Parameter Category | Detailed Specifications |

|---|---|

| Basic Information | Product Name: Hello-FPGA-FMC-SFP-X4 10G Fiber Module; Compliance Standard: VITA 57.1 |

| Interface Specifications | Interface Type: FMC LPC (Low Pin Count); Connector Model: ASP-134488-01; Pin Count: 160 Pins |

| Signal & Rate | SFP+ Interface: 4 Ports, each with independent TX/RX differential channels; Max Transmission Rate: 10Gb/s; Test Rate: 10Gbps |

| Onboard Components | Crystal Oscillator: Dual high-precision crystal oscillators of 125MHz + 156.25MHz; Storage Chip: 24LC04 I2C EEPROM (Supporting I²C Protocol) |

| Compatible Module Types | Optical Modules: SFP+ SR (multi-mode ≤300m), LR (single-mode ≤10km), ER (single-mode ≤40km); Copper Cables: SFP+ DAC (1~10m); Supporting Hot-Swapping |

| Test Performance | Supported Tools: Xilinx IBERT (Bit Error Rate Test), Eye Diagram Analysis; Target Bit Error Rate (BER): ≤8.3×10⁻¹²; Eye Diagram Opening: 66.67% UI |

| Power Supply Compatibility | Supported Voltage: +3.3V, +12V provided by carrier board, VADJ adjustable voltage (1.2V/1.8V/2.5V, etc.) |

| Core Functions | 4-Port 10G Signal Parallel Transmission, I²C Automatic Module Identification, Link Status Detection (TX_DIS/RX_LOSS), Hot-Swapping |

| Software Compatibility | Development Environment: VIVADO; Debugging Tools: IBERT (Bit Error Rate Test), Eye Diagram Scanning, Jitter Analysis |

| Mechanical Dimensions | 69mm×82mm (Standard FMC Single Slot Size) |

Product Dimension Diagram

Standard FMC Size: 69mm×82mm (Unit: mm)

Safety Warnings (Must Read)

- Do NOT hot-plug the board: Power off the FPGA carrier board and unplug the power cable before installation/removal. Hot-plug operation will directly damage the board, carrier board or connected devices.

- Take ESD Protection Measures: Release static electricity from the human body (anti-static wristband is recommended) before touching the electronic components of the product. Static electricity can cause permanent damage to precision components.

- Standard Module Installation: Push SFP+ optical modules/cables gently to the locked position during insertion to avoid interface damage caused by violent plugging; perform hot-swapping operation only when the device is in idle state.

- Power Supply Safety: Connect power supply in strict accordance with the power supply requirements of the carrier board, ensure that the voltage is stable within the rated range, and avoid circuit burnout caused by overvoltage or reverse connection.

- Environmental Requirements: Avoid storing or using the product in places with water splashing, direct sunlight, strong electric/magnetic fields, strong vibration, or heavy dust to ensure long-term stable operation of the device.

Quick Start Guide

- Hardware Connection: Insert the Hello-FPGA-FMC-SFP-X4 daughter card into the FMC LPC slot of the FPGA carrier board correctly, tighten the fixing screws; insert SFP+ optical modules or cables according to requirements to ensure firm connection.

- Power Supply Configuration: Confirm that the FPGA carrier board is powered normally to ensure stable working voltage of the daughter card, and configure VADJ voltage (1.2V/1.8V/2.5V, etc.) according to I/O level requirements.

- Software Configuration: Launch Xilinx VIVADO development environment, load the board configuration file, and configure parameters such as clock and rate according to test requirements.

- Test & Verification: Enable IBERT tool for Bit Error Rate Test, Eye Diagram Scanning, etc., confirm that the link transmission status is normal and the Bit Error Rate meets the standard (≤8.3×10⁻¹²).

- System Deployment: After passing the test, deploy the device to the target scenario, fix the cables and board firmly, ensure good heat dissipation, and complete system integration.

- Maintenance & Upgrade: If SFP+ modules need to be replaced, the hot-swapping function is supported, which can be replaced directly without turning off the power supply of the entire system.

Typical Application Scenarios