CXP2.0 HOST FPGA IP

The CXP2.0 HOST FPGA IP is a high‑performance host IP core compliant with the CoaXPress V2.0 standard, providing high‑throughput image and control transmission for machine vision and industrial imaging systems.

CXP2.0 HOST FPGA IP

Product Overview

CXP2.0 HOST FPGA IP is a high-performance host IP core compliant with the CoaXPress V2.0 standard, providing high-throughput image data and control command transmission for machine vision and industrial imaging systems.

Key Features

- Compliant with CoaXPress V2.0 (JIIA NIF‑001‑2019), backward compatible with V1.1 and V1.0

- Supports high-speed downlink up to CXP‑12 and 41.6 Mbps uplink

- Supports 1/2/4/8-lane configurations for high-bandwidth transmission

- Supports up to 8 parallel video streams for multi-camera/sensor systems

- Uses FPGA embedded high-speed transceivers as PHY layer for robust design

- User control bus: AXI4 interface

- User data bus: dedicated video stream interface

- Dedicated GPIO and trigger interface for downstream device control

Supported Devices

- Supports all Xilinx FPGA families

- Validated platforms: KC705, KCU105, ZCU102, ALINX Z19, Z7P, AXKU040, etc.

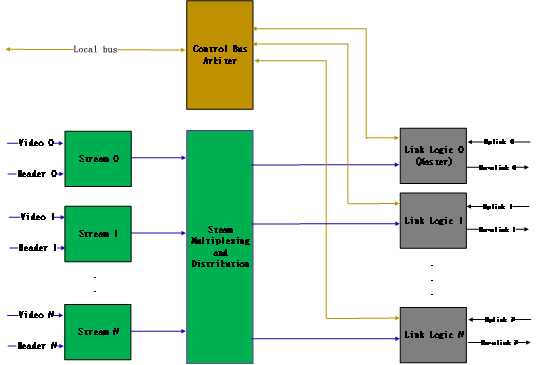

Architecture Diagram

CXP2.0 HOST FPGA IP Data Flow Diagram

CXP2.0 HOST FPGA IP Top-level Interface & Pin Definition