CXP2.0 DEVICE FPGA IP

The CXP2.0 DEVICE FPGA IP is a high-performance intellectual property core designed to comply with the CoaXPress V2.0 standard, providing reliable and high-throughput data transmission capabilities for FPGA-based imaging and industrial control applications.

CXP2.0 DEVICE FPGA IP

Overview

CXP2.0 DEVICE FPGA IP is a high-performance IP core compliant with CoaXPress V2.0 standard, providing reliable and high-throughput data transmission for FPGA-based imaging and industrial control applications.

Key Features

- Compliant with CoaXPress V2.0 (JIIA NIF-001-2019), backward compatible with V1.1 and V1.0

- Supports CXP-12: up to 12.5Gbps high-speed link and 41.6Mbps low-speed link

- Supports multiple CoaXPress links for high-bandwidth data transmission

- Supports multi-video streams for direct connection to multiple sensors

- Supports up to 4 parallel CoaXPress links for higher throughput

- Control via simple local burst bus, no CPU required, low resource usage

- Highly configurable video interface, direct connection to various image sensors

- Built-in CRC-32 generator and checker for data integrity

Compatibility

- Supports all Xilinx FPGA families

- Validated platforms: KC705, KCU105, ZCU102

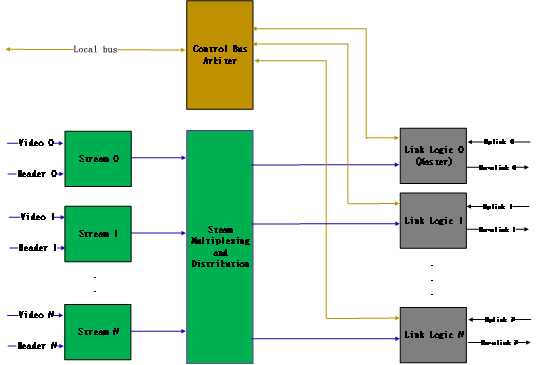

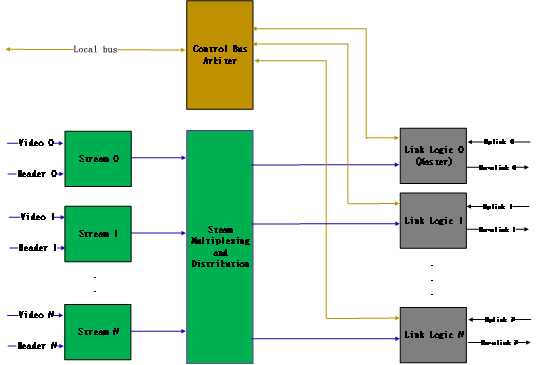

Block Diagram

Figure 1 CXP2.0 DEVICE FPGA IP Data Flow Block Diagram